はじめに

以下の全3回に分けて、Adeiaの企業分析をおこなっていきます。今回は、技術紹介編です。Adeiaがライセンス提供するウェーハ接合技術、特にハイブリッドボンディング技術がどのようなものか、紹介していきます。公開する順番は適当です。。。

*基礎編:そもそも、ウェーハ接合・ハイブリッドボンディングとは?その応用は?

(Adeiaの企業分析とは別枠)

沿革編:Adeiaのウェーハ接合IP事業が現在に至るまでの沿革。

技術紹介編:Adeiaがライセンス提供するウェーハ接合技術、特にハイブリッドボンディング技術がどのようなものか

提携企業編:Adeiaが自社のハイブリッドボンディング技術をライセンス提供している企業を紹介

Adeiaがライセンス提供するウェーハ接合技術

adeia.com/resources/introducing-zibond-and-dbi-technologies

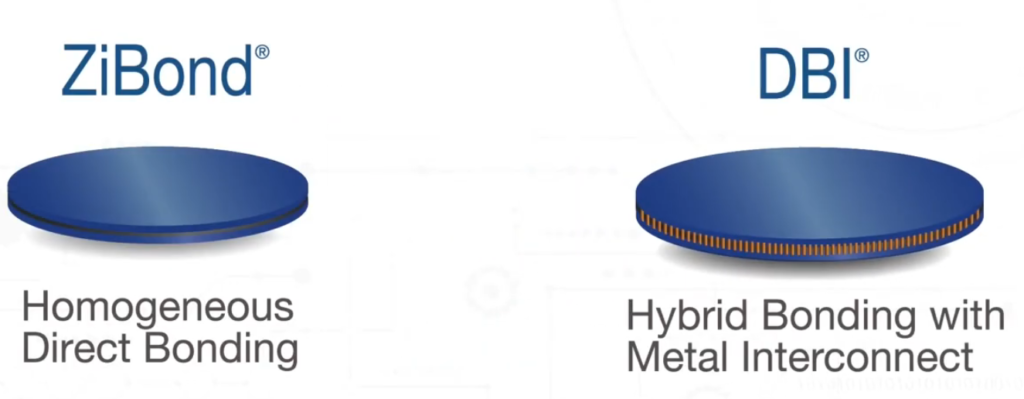

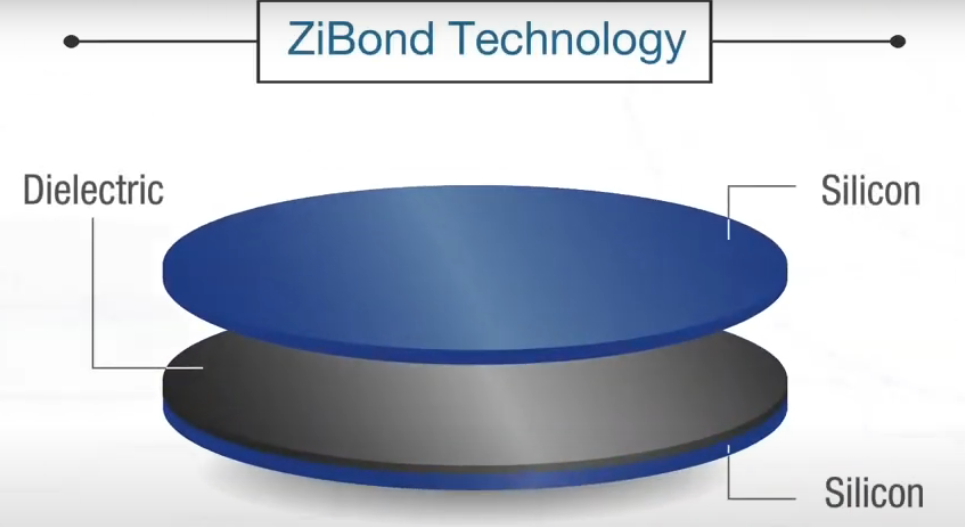

ZiBond®

ZiBond®は、ウェーハ同士の接合(Wafer-to-Wafer)に最適な低温直接接合技術です。熱膨張係数が同じまたは異なる半導体ウェハーやダイ間に強力な接合を形成します。この技術は、イメージセンサー、MEMS、さまざまなRFフロントエンドデバイスに適用されています。後述のDBIが接合と同時に電気的接続を確保しているのに対して、Zibondは電気的な接続ではない機械的な接合のみとなります。

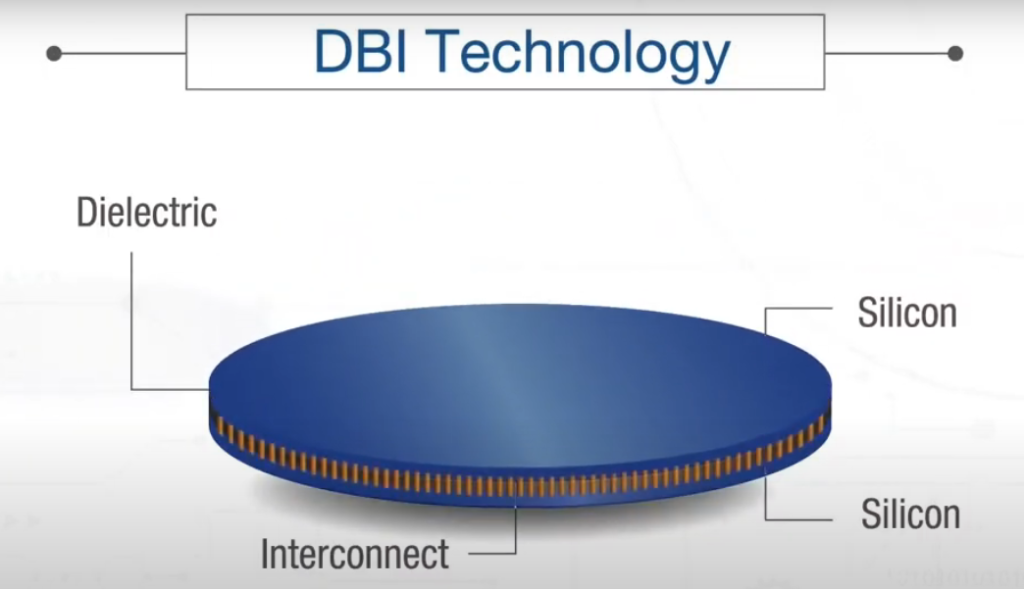

DBI®

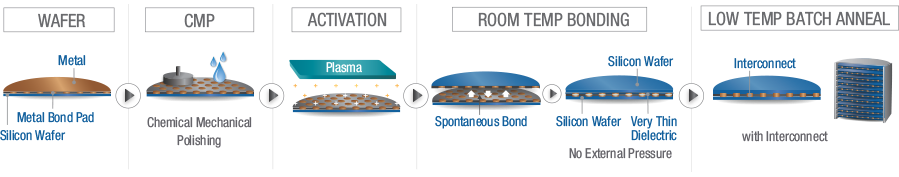

DBI®は、ウェーハ同士の接合(Wafer-to-Wafer)に最適な低温ハイブリッドダイレクトボンディング技術です。前述のZiBond®が単純な接合であるのに対して、DBI®は電気的相互接続を伴う wafer-to-wafer ボンディングです。BSI Image Sensor, DRAM, MEMS, RFの製造プロセスに対して応用可能です。具体的なプロセスフローは以下の通りです。

- ウェーハ上の酸化シリコン(SiO2)等の誘電体層に、銅またはニッケルの埋め込み電極を形成する。

- ウェーハ表面をCMP(化学機械研磨)プロセスで研磨する。同時に、電極部分がわずかに凹む(ディッシング)。

- 表面をエッチングした後、窒素(N)を含むアンモニア系ガスで前処理を施す。

- 室温環境下で、2枚のウェーハの位置を金属電極が合うように調整(アライメント)し対向接触させると、向かい合う前処理済みの誘電体(SiO2など)同氏が共有接合し、永久接合が形成される。

この際、金属電極間は前述のディッシングにより隙間が空いた状態となる。 - 室温以上の比較的低温でのバッチアニール後、向かい合う金属電極の両端が熱膨張して接触し、接合界面で相互拡散することで、金属配線接合が形成される。

Dbi Wafer-to-Wafer Hybrid Bonding (adeia.com)

DBI® Ultra

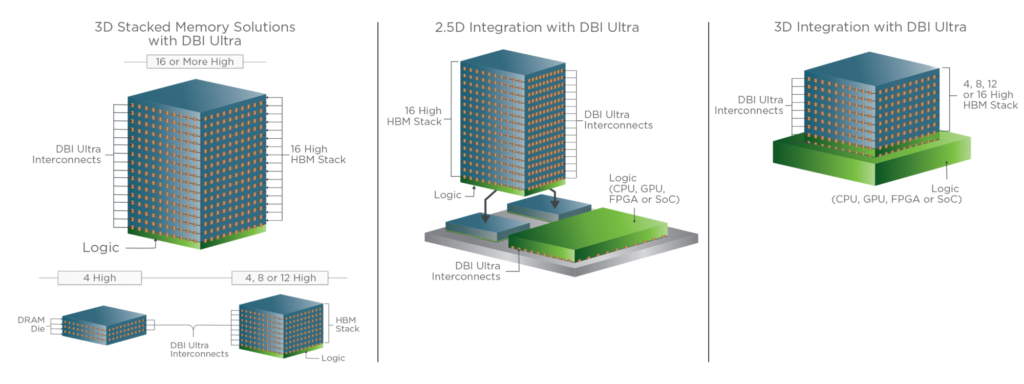

DBI® Ultraは、ダイとウェーハ同士の接合(Die-to-Wafer)およびダイ同士の接合(Die-to-Die)のハイブリッドボンディング技術です。銅ピラーやアンダーフィルを不要にすることで、従来のアプローチと比較して飛躍的に薄いスタックを可能にします。また、1 µmインターコネクトピッチまで容易に微細化しながら、同一または異なるサイズのダイ、微細または粗いウェーハプロセス技術ノードで処理されたダイ、同一または異なるウェーハサイズで製造されたダイのスタッキングを可能にします。

応用先としては、DRAM、マイクロプロセッサ、グラフィックス・プロセッサ、SoCなどの大型ダイに適しています。特に、4、8、12、16ダイ以上の高帯域幅メモリー(HBM)スタック、高性能コンピューティングのためのCPU、GPU、FPGA、SoCとメモリーの2.5D/3D統合に応用が可能です。また、既知の良品ダイを他の既知の良品ダイにボンディングすることができ、高歩留まりのマルチダイスタック2.5Dおよび3Dアセンブリを可能にします。

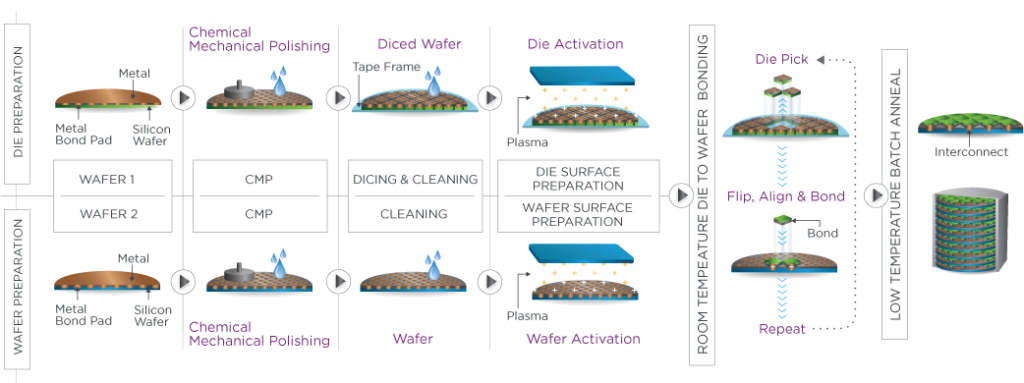

具体的なプロセスフローは以下の図に示す通りです。基本的なプロセスは前述のDBI®と同じですが、DBI® Ultraではダイ(Die, チップ個片)の切り出し工程およびフリップ・アライン工程が含まれます。

DBI Die-to-Wafer Hybrid Bonding (adeia.com)

文献・特許

Zibond特許:

US7387944B2 – Method for low temperature bonding and bonded structure – Google Patents

DBI特許:

US6962835B2 – Method for room temperature metal direct bonding – Google Patents

関連文献

Low Temperature Hybrid Bonding for Die to Wafer Stacking Applications

コメント